Digital Systems

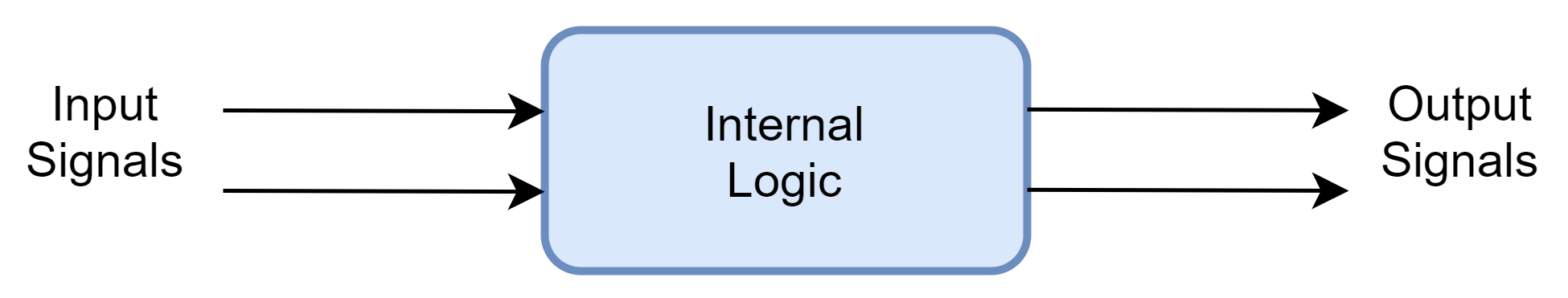

VHDL is a hardware descriptive language, which means that the code describes how to configure the digital hardware within an FPGA. The digital hardware makes up a digital system, which is made up of inputs, outputs, and internal logic. Below is a diagram of a basic system. Internal logic operates on the input signals to produce the output signals.

The Entity

Just like a physical system of digital logic, a VHDL program will have inputs, outputs, and internal logic. The entity is a code structure that represents the digital system. The inputs and outputs are defined as ports within the entity. In general, ports are defined as either "in" or "out" and a data type must be specified. In the example below, two inputs are defined, "Button1" and "Switch1", and one output is defined, "Led1". All three are std_logic types, which means they only hold logic values of 1 or 0. The LedController is the entity and corresponds to the box in the system diagram.

entity LedController is

port (

Button1 : in std_logic;

Switch1 : in std_logic;

Led1 : out std_logic

);

end LedController;

It's important to note that VHDL requires semi-colons between statements. Note the word "between", because when there is no statement following the current statement, there should be no semi-colon. In line 5 of the above example, the semi-colon is omitted since there is no following statement inside the port definitions.

The ports have now been defined, but the internal logic has not yet been defined. However, defining the internal logic takes several steps in VHDL, so this will be covered over the course of the next few lessons.